Заглавная страница Избранные статьи Случайная статья Познавательные статьи Новые добавления Обратная связь FAQ Написать работу КАТЕГОРИИ: ТОП 10 на сайте Приготовление дезинфицирующих растворов различной концентрацииТехника нижней прямой подачи мяча. Франко-прусская война (причины и последствия) Организация работы процедурного кабинета Смысловое и механическое запоминание, их место и роль в усвоении знаний Коммуникативные барьеры и пути их преодоления Обработка изделий медицинского назначения многократного применения Образцы текста публицистического стиля Четыре типа изменения баланса Задачи с ответами для Всероссийской олимпиады по праву

Мы поможем в написании ваших работ! ЗНАЕТЕ ЛИ ВЫ?

Влияние общества на человека

Приготовление дезинфицирующих растворов различной концентрации Практические работы по географии для 6 класса Организация работы процедурного кабинета Изменения в неживой природе осенью Уборка процедурного кабинета Сольфеджио. Все правила по сольфеджио Балочные системы. Определение реакций опор и моментов защемления |

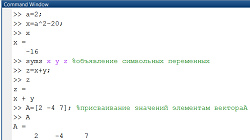

Программное управление контроллером ПДПСодержание книги

Поиск на нашем сайте

Программное управление контроллером ПДП осуществляется через порты ввода-вывода. Доступ к каждому регистру контроллера может быть осуществлен через свои порты ввода-вывода. Распределение адресов и описание внутренних регистров первого и второго контроллера ПДП приведено в таблице 2.

Таблица 2. Регистры контроллера ПДП 8237А. 8237#1 |

8237#2 |

R / W | Назначение регистров | ||||

| 008h | 0D0h | W | Регистр команд (Command Register) Биты: 7=1 – активный уровень DACK – высокий 6=1 – активный уровень DRQ – высокий 5=1 – режим расширенной записи 4=1 – циклический приоритет 3=1 – укороченный цикл обмена 2=1 – запрет работы контроллера 1=1 – фиксация адреса 0 канала 0=1 – передача память-память (в PC не используется) | |||||

| 008h | 0D0h | R | Регистр состояния каналов (Status Register) Биты 7..4 запросы каналов 0-3 Биты 3..0 завершение цикла каналов 0-3 | |||||

| 009h | 0D2h | W | Регистр запросов (Request Register) Биты 7..3 – не используются 2=1 – установка/ =0 – сброс бита запроса 1..0 – выбор канала (00=0, 01=1, 10=2, 11=3) | |||||

| 00Ah | 0D4h | W | Регистр маски - Single Mask Bit Register Биты 7..3 – не используются 2=1 – установка/ =0 – сброс бита маски 1..0 – выбор канала (00=0, 01=1, 10=2, 11=3) | |||||

| 00Bh | 0D6h | W | Регистр режима работы канала (Mode Register) Биты 7..6 – режим передачи (00- по запросу, 01- одиночный, 10- блочный, 11- каскадирование) 5=1 – инкремент / =0 – декремент адреса 4=1 – разрешение автоинициализации 3..2 – тип передачи (00- холостой, 01-запись, 01- чтение, 11- не исп.) 1..0 – выбор канала (00=0, 01=1, 10=2, 11=3) | |||||

| 00Ch | 0D8h | W | Сброс триггера младшего/старшего байта – Clear Byte Pointer Flip/Flop | |||||

| 00Dh | 0DAh | W | Общий сброс 8237А - Master Clear (вывод любого байта в регистр вызывает сброс) | |||||

| 00Eh | 0DCh | W | Общий сброс масок всех каналов – Clear Mask Register (вывод любого байта в регистр вызывает сброс) | |||||

| 00Fh | 0DEh | W | Регистр масок всех каналов - All Mask Register Bits Биты 7..4 – не используются 3..0 – маски каналов 0-3 (0-канал разрешен, 1- маскирован) | |||||

| Регистры управления каналами второго контроллера | ||||||||

| - | 0C0h, 0C4h, 0C8h, 0CCh | W | Запись начального адреса в регистр начального адреса (Base Address Register) и регистр текущего адреса канала (Current Address Register) 4,5,6,7 | |||||

| - | 0C0h, 0C4h, 0C8h, 0CCh | R | Чтение начального адреса из регистра начального адреса канала (Current Address Register) 4,5,6,7 | |||||

| - | 0C2h, 0C6h, 0CAh, 0CEh | W | Запись в регистр начального счетчика циклов (Base Word Count Register) и в регистр текущего счетчика циклов канала (Current Word Count Register) 4,5,6,7 | |||||

| - | 0C2h, 0C6h, 0CAh, 0CEh | R | Чтение текущего значения из регистра текущего счетчика циклов канала (Current Word Count Register) 4, 5, 6, 7 | |||||

| - | 089h, 08Bh, 08Ah, 08Fh | W | Задание номера страницы для канала 6,5,7,4 | |||||

Каналы 4 - 7 предназначены для обмена 16-разрядными словами. В связи с этим возникает ряд отличий в работе с этими каналами:

- бит 0 в данных, заносимых в регистры начального и текущего адреса, всегда подразумевается равным 0, поэтому через эти регистры передаются биты 1 - 16 полного 23-разрядного адреса (а не биты 0 - 15 полного 20-разрядного адреса, как это реализовано на ХТ - подобных ПЭВМ). По этой же причине в страничные регистры каналов 4 - 7 заносятся биты 17 - 23 полного адреса, а не биты 16 - 23, как это надо сделать при работе с каналами 0 - 3;

- поскольку передача осуществляется 16-разрядными словами, в регистры текущего и начального счетчика циклов заносится не число байт, а число слов, уменьшенное на единицу;

- размеры страниц памяти, в пределах которых возможен обмен в течение одной передачи, составляют 2000h байтов.

Описание регистров

Регистр начального адреса (Base Address Register). В этом регистре задается стартовый адрес ОЗУ, с которого начинается передача. Регистр содержит 16 разрядов и определяет адрес внутри заданной страницы памяти размером 64К. Задание номера страницы памяти осуществляется через специальные страничные регистры (Page Registers), поддерживаемые внешней логикой.

Каждый канал ПДП имеет свой регистр начального адреса и страничный регистр. Такое деление памяти на страницы не позволяет осуществить обмен с блоком памяти, находящимся на пересечении двух страниц. Каждая страница начинается с сегментного адреса, кратного 1000h (0, 1000h, 2000h,..., 9000h).

|

| Поделиться: |